Flip-Flop J-K

|

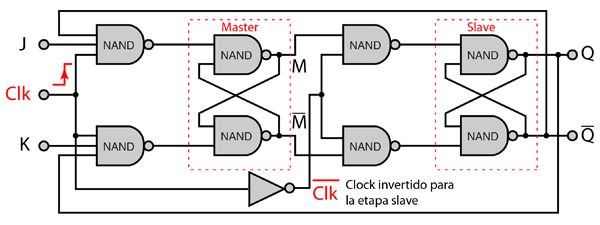

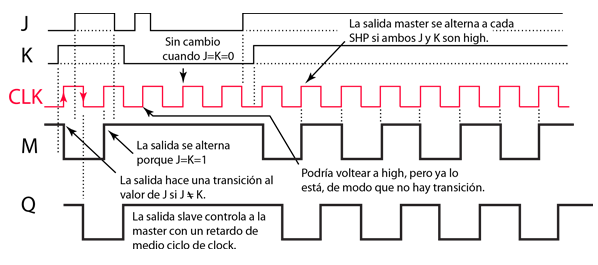

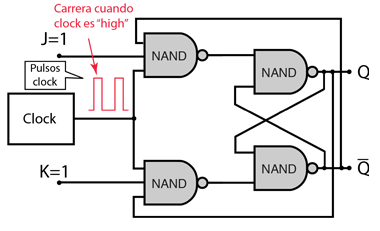

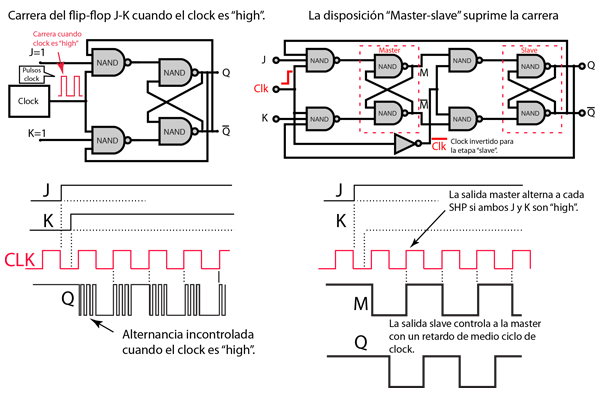

El "flip-flop" J-K, es el mįs versįtil de los flip-flops bįsicos. Tiene el carįcter de seguimiento de entrada del flip-flop D sincronizado, pero tiene dos entradas, denominadas tradicionalmente J y K. Si J y K son diferentes, la salida Q toma el valor de J durante la subida del siguiente pulso de sincronismo.

|

|

Si J y K son ambos low (bajo), entonces no se produce cambio alguno. Si J y K son ambos high (alto), entonces en la siguiente subida de clock la salida cambiarį de estado. Puede realizar las funciones del flip-flop set/reset y tiene la ventaja de que no hay estados ambiguos. Puede actuar tambien como un flip-flop T para conseguir la acción de permutación en la salida, si se conectan entre sķ las entradas J y K. Esta aplicación de permutar el estado, encuentra un uso extensivo en los contadores binarios.

| Flip-Flops |

Conceptos de Electrónica

Circuitos Digitales

Operaciones Secuenciales

Aplicaciones del Flip-Flop J-K

| HyperPhysics*****Electricidad y Magnetismo | M Olmo R Nave |